# INSTITUTO SUPERIOR TÉCNICO

## Arquitectura de Computadores

Ano Lectivo de 2008/2009

2º Semestre

1º Teste

20 de Abril de 2009

Duração: 1h30+0h30

- O teste é sem consulta, apenas tem disponível o anexo que lhe deverá ter sido entregue com o teste. Por favor, não escreva nesse anexo e devolva-o no final do teste.

- Resolva o teste no próprio enunciado, o espaço reservado para cada pergunta é suficiente para a sua resposta. Tenha em atenção que cada grupo deve ficar em folhas separadas. Utilize as costas das folhas para rascunho.

- Identifique todas as folhas que entregar, folhas não identificadas não serão cotadas!

- Responda ao teste com calma. Se não sabe responder a uma pergunta, passe à seguinte e volte a ela no fim.

#### I. (1 + 1 + 1 + 2 = 5 val.)

Considere os seguintes valores para os registos do processador P3:

| R1    | R2    | R3    | R4    | R5    | R6    | R7    | PC    | SP    | RE    |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4BF9h | CAB4h | 01ADh | 0548h | EC3Fh | 5BFEh | 89D7h | 88DDh | 7CFBh | 001Ch |

Para as perguntas 1, 2 e 3, indique quais são os novos valores, em hexadecimal, de todos (**e apenas**) os registos que são escritos na execução de cada instrução. Use ? para indicar que não tem informação suficiente para determinar o novo valor de um registo.

As perguntas são independentes, isto é, assuma como **valores iniciais** para cada pergunta os indicados na tabela acima.

1. XOR R7,R1

|             | ,            |    |    |    |    |    |    |    |    |

|-------------|--------------|----|----|----|----|----|----|----|----|

| R1          | R2           | R3 | R4 | R5 | R6 | R7 | PC | SP | RE |

|             |              |    |    |    |    |    |    |    |    |

| 2. POI      | 2. POP M[R5] |    |    |    |    |    |    |    |    |

| R1          | R2           | R3 | R4 | R5 | R6 | R7 | PC | SP | RE |

|             |              |    |    |    |    |    |    |    |    |

| 3. BR.NO -1 |              |    |    |    |    |    |    |    |    |

| R1          | R2           | R3 | R4 | R5 | R6 | R7 | PC | SP | RE |

|             |              |    |    |    |    |    |    |    |    |

- 4. Na execução da instrução DIV R0, M[R2+4Ah], indique na tabela seguinte qual é a sequência de acessos à memória, especificando o valor do barramento de endereços, do barramento de dados e tipo de acesso (leitura/escrita).

- Nota 1: a tabela tem 5 posições, utilize apenas as que achar necessárias.

- Nota 2: utilize os valores iniciais dos registos indicados na tabela no cimo desta página.

- Nota 3: use ? para indicar que não tem informação suficiente para determinar um dado valor.

|   | Endereço | Dados | Leitura/Escrita |

|---|----------|-------|-----------------|

| 1 |          |       |                 |

| 2 |          |       |                 |

| 3 |          |       |                 |

| 4 |          |       |                 |

| 5 |          |       |                 |

| Númoros | Nome:  | 1/6 |

|---------|--------|-----|

| Número: | NOIDE. | 1/0 |

### II. (3 + 1,5 = 4,5 val.)

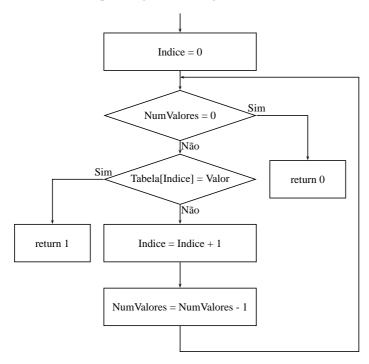

Considere uma rotina descrita pelo seguinte fluxograma:

1. Escreva esta rotina em Assembly do P3. Assuma que os parâmetros de entrada e de saída são passados pela pilha, colocados na seguinte ordem: saída; Tabela; NumValores; Valor.

2. Descreva a alto nível, e de forma sucinta, a função realizada por esta rotina.

Número:\_\_\_\_\_\_ Nome:\_\_\_\_\_

2/6

### III. (1,5+1+1,5+1,5=5,5 val.)

Considere o seguinte excerto de um programa para o processador P3 que implementa um relógio digital, com indicação das horas e minutos (ex: 22:54).

```

BASETIME

EQU

TIMER_UNITS EQU

FFF6h

TIMER_CTRL EQU

FFF7h

ORIG 0000h

Timer:

MOV

R1, BASETIME

MOV

M[TIMER_UNITS], R1

MOV

R1, 1h

M[TIMER_CTRL], R1

MOV

R7, Count

MOV

M[SP+1], R7

XCH

PUSH R7

PUSH R1

Count:

INC

M[Minutes]

R1, 60

M[Minutes], R1

MOV

CMP

BR.N ExitCount

MOV

M[Minutes], R0

INC

M[Hours]

MOV

R1, 24

M[Hours], R1

CMP

BR.N ExitCount

VOM

M[Hours], R0

ExitCount:

POP

R1

RET

Loop:

CALL WriteHours

CALL WriteMinutes

BR

Loop

```

1. Indique, justificando, a funcionalidade deste programa. Em particular, explique em que circunstâncias é que a rotina Count é executada.

2. Indique o valor com que deve ser inicializada a constante BASETIME. Justifique a sua resposta.

|   | inicialização necessários para que a rotina Timer fique associada à in 15. Exemplifique através de instruções/pseudo-instruções do Assembly |     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

| • | início da execução, verificou-se que o programa apresenta, em certas ortamento anómalo. Identifique uma situação em que tal anomalia po     |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   |                                                                                                                                             |     |

|   | Nome:                                                                                                                                       | 4/6 |

### IV. (1+1+3=5 val.)

| 1. | Em linguagem C, a declaração de uma matriz é dada por short | int | A[5][8];. |

|----|-------------------------------------------------------------|-----|-----------|

|    | A declaração equivalente em Assembly do P3 será:            |     |           |

Determine o endereço de memória onde se encontra o elemento da matriz A[4][3].

2. Utilizando uma sequência de, no máximo, 2 instruções Assembly do P3, indique 3 formas diferentes de colocar o valor 0 no registo PC. O valor de todos os bits de estado e de todos os outros registos deve ficar igual. A mesma instrução não pode ser repetida em nenhuma das alternativas, e só pode usar saltos condicionais no máximo numa das alternativas.

Número:\_\_\_\_\_\_Nome:\_\_\_\_\_

5/6

| a) É possível representar de forma exacta no P3, usando vírgula fixa, o valor 18,75.  Verdadeiro Falso Depende  b) Após a execução da seguinte sequência de instruções no P3, os R1 e R2 ficam com o n valor.  DSI POP R1 MOV R2, M[SP]  Verdadeiro Falso Depende  c) Dentro de uma rotina de tratamento a uma interrupção, as instruções STC e OR M[SP+são equivalentes.  Verdadeiro Falso Depende  d) No processador P3, um possível opcode para uma nova instrução de 2 operandos, op1, op2, é 5Fh.  Verdadeiro Falso Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.  Verdadeiro Falso Depende |                    | tes afirmações são verdadei<br>valores; o valor mínimo da | _                      | ergunta certa +0,6 val.; c |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------|------------------------|----------------------------|

| b) Após a execução da seguinte sequência de instruções no P3, os R1 e R2 ficam com o no valor.  DSI POP R1 MOV R2, M[SP]  Verdadeiro Falso Depende  c) Dentro de uma rotina de tratamento a uma interrupção, as instruções STC e OR M[SP+são equivalentes.  Verdadeiro Falso Depende  d) No processador P3, um possível opcode para uma nova instrução de 2 operandos, op1, op2, é 5Fh.  Verdadeiro Falso Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                          | a) É possível repr | esentar de forma exacta no                                | P3, usando vírgula fix | a, o valor 18,75.          |

| valor.  DSI POP R1 MOV R2, M[SP]  Verdadeiro Falso Depende  c) Dentro de uma rotina de tratamento a uma interrupção, as instruções STC e OR M[SP+são equivalentes.  Verdadeiro Falso Depende  d) No processador P3, um possível <i>opcode</i> para uma nova instrução de 2 operandos, op1, op2, é 5Fh.  Verdadeiro Falso Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                                                                                                           |                    | Verdadeiro                                                | Falso                  | Depende                    |

| POP R1 MOV R2, M[SP]  Verdadeiro Falso Depende  c) Dentro de uma rotina de tratamento a uma interrupção, as instruções STC e OR M[SP+são equivalentes.  Verdadeiro Falso Depende  d) No processador P3, um possível <i>opcode</i> para uma nova instrução de 2 operandos, op1, op2, é 5Fh.  Verdadeiro Falso Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                                                                                                                       |                    | ão da seguinte sequência de                               | instruções no P3, os F | R1 e R2 ficam com o mes    |

| c) Dentro de uma rotina de tratamento a uma interrupção, as instruções STC e OR M[SP+são equivalentes.  Verdadeiro  Falso  Depende  d) No processador P3, um possível <i>opcode</i> para uma nova instrução de 2 operandos, op1, op2, é 5Fh.  Verdadeiro  Falso  Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                                                                                                                                                                   |                    | POP                                                       |                        |                            |

| são equivalentes.  Verdadeiro  Falso  Depende  d) No processador P3, um possível <i>opcode</i> para uma nova instrução de 2 operandos, op1, op2, é 5Fh.  Verdadeiro  Falso  Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                                                                                                                                                                                                                                                        |                    | Verdadeiro                                                | Falso                  | Depende                    |

| d) No processador P3, um possível <i>opcode</i> para uma nova instrução de 2 operandos, op1, op2, é 5Fh.  Verdadeiro  Falso  Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                                           | nterrupção, as instruç | ões STC e OR M[SP+2]       |

| op1, op2, é 5Fh.  Verdadeiro  Falso  Depende  e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    | Verdadeiro                                                | Falso                  | Depende                    |

| e) A instrução BR. Z 0 é em tudo equivalente à instrução NOP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                  | •                                                         | para uma nova instru   | ıção de 2 operandos, XI    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    | Verdadeiro                                                | Falso                  | Depende                    |

| Verdadeiro Falso Depende                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e) A instrução BR  | Z 0 é em tudo equivalent                                  | e à instrução NOP.     | _                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    | Verdadeiro                                                | Falso                  | Depende                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                                                           |                        |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                                                           |                        |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                                                           |                        |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                                                           |                        |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                                                           |                        |                            |